全球首款!基于CMOS工艺的国产化多频多模线性PA落地问世!

当前,随着5G、WiFi等技术不断演进与应用,射频前端芯片正迎来新的发展机遇。一方面,受益5G频段增加,射频前端芯片应用领域进一步拓展,市场呈现大幅增长态势;另一方面射频前端芯片技术高频化和集成化,为工艺技术发展带来新的变革。尽管以GaAs工艺为代表的III-V族PA仍然为射频前端芯片主流技术,但硅基CMOS PA凭借低成本、高集成度、漏电流低、导热性好等优势,正从非主流应用地位转变,将在WiFi、物联网等应用领域大放异彩。

2000年以来,全球大批工程师、科学家对CMOS PA技术进行了大量的产业化应用研究,虽曾在线性CMOS PA产业化折戟,但对CMOS工艺的执着从未间断。过去十年,一批国内企业开始在CMOS PA技术上有所建树,特别在低频 2G、3G上占有一定的市场地位。而一些射频前端企业也在持续研究4G线性CMOS PA,取得了一定发展成绩。地芯科技就是典型的代表,并将于5月18日在上海发布全球首款线性4G CMOS PA。

PA技术路线之争

射频PA是通信链路中至关重要的器件,负责将发射链路中的射频信号做最后的放大,输送到天线,也是整个通信链路中功耗最大的器件之一。

在低频 2G、3G时代,CMOS PA 曾经凭借低成本优势,以及易于与传统硅基数字电路进行集成,也出现了短暂的发展荣光。但从3G时代后,GaAs(砷化镓)工艺凭借击穿电压、输出功率等优势,开始替代CMOS PA成为主流。

相较于GaAs PA,CMOS PA主要差距在于材料上的劣势。具体体现在:一是电流密度。GaAs的电子迁移率比Si高出很多,因此HBT器件相较CMOS器件的电流密度也要高出很多。而要达到相当的增益,往往需要更大的CMOS器件或者更多的级联才能匹配到GaAs PA的水平。

二是Vknee电压和效率。GaAs HBT的I-V curve表现出很低的Vknee电压,在CMOS器件中随着Vds平缓增加的电流,导致了较高的Vknee电压。这使得在饱和功率下,PA的效率大打折扣,同时也体现出CMOS管子的源漏寄生电阻比较大。

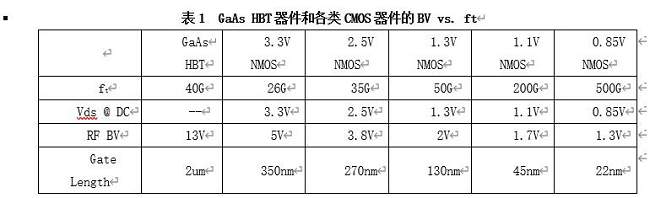

三是击穿电压(BV)vs. 截止频率(ft)。CMOS工艺的频率响应和工艺节点强相关,PA一般工作在ft十分之一的频率比较容易实现设计。GaAs HBT的ft在40G左右,比较适用于sub 6G以下的大部分应用;0.35um的CMOS器件ft在26G左右,45nm的器件可以达到超过200G的ft,因此可以触及毫米波的应用场景,22nm更是可以达到接近500G的截止频率。因此CMOS工艺随着工艺节点缩微化,可以工作在极高的频率,但最大的硬伤和痛点在击穿电压。

资料来源:地芯科技

四是非线性问题。CMOS器件大部分的非线性来自于栅极电容随电压变化的改变。由于CMOS器件的电流密度小以及漏极寄生电阻大,输出超过瓦级的功率需要很大尺寸的场效应管,这便直接造成非线性的加剧。

不过,CMOS PA也并非完全劣势,作为集成电路中最为广泛使用的工艺技术,其相较于GaAs等III-V族PA也具有诸多优势,具体如下:

一是集成度。GaAs PA往往需要多颗工艺不同的Die的合封(SiP)来实现逻辑控制、开关切换、功率功放、接收放大(FEM)等多种射频前端的功能,结构复杂,成本高昂。而分立的PA或者FEM有机会通过单一CMOS工艺的Die实现上述全部功能,在一致性、封装可靠性以及成本上,都具有很大的优化和提升空间。

二是低成本。成本是CMOS工艺最大的优势之一,一张12英寸的CMOS晶圆的成本往往与6寸的GaAs晶圆价格相当,面积则是4倍。CMOS工艺是最主流的集成电路制程,供应链和产能丰富,这也是成本方面有巨大优势的原因之一。

三是器件特性。CMOS工艺在器件特性上主要体现在漏电流低和导热性好。CMOS工艺是天生为数字电路而生的开关器件,在关断模式下漏电很低,比GaAs器件有数量级的优势。Si的热导率是GaAs的3倍,在热性能方面优势明显。

四是设计灵活性。CMOS工艺的开关特性和丰富的器件种类为设计师带来了无限的创造空间。二十多年来,工业界和学术界不遗余力地在CMOS PA的设计上贡献智慧:模拟/数字预失真技术、数字PA技术、负载牵引技术、数字校准技术等,都可以为CMOS器件的劣势补上短板,并带来更多的灵活性、可配性和一致性的提升。

因此,综合上述,CMOS PA设计最大的挑战来自击穿电压低和线性度差,而效率和电流密度的劣势对线性PA设计的影响相对较弱。

为何线性COMS这么难?

通过上述GaAs PA和CMOS PA对比,可以得出结论:线性CMOS PA的设计主要考虑如何提高击穿电压以及补偿器件自身的非线性。因此,在击穿电压、非线性、高频等优势的支持下,目前III-V族PA在4G、5G大规模应用。

这里要特别提一下CMOS工艺的非线性问题。一直以来,CMOS工艺的非线性特性就是其在4G、5G应用上的最大技术挑战之一,甚至芯片巨头高通也因无法解决4G CMOS PA的线性问题“止步于前”。

据悉,射频PA可分为饱和PA和线性PA两种架构,分别对恒包络(PAR=0dB)的调制信号(FSK、PSK、GMSK等),存在幅度调制的通信信号(QAM、ASK、OFDM、CDMA等)进行放大。2G GSM、BLE、Zigbee等通信制式是恒包络信号,饱和PA即可满足放大需求;CDMA、3G WCDMA、4G LTE、5G、WiFi4/5/6等为幅度调制的宽带信号,需要线性PA进行保真放大。

作为摩尔定律的载体,CMOS工艺在过去的数十年飞速发展,已经成为最成熟的工艺,基于8寸/12寸的大硅片,各大晶圆代工厂的产能丰富。因此,CMOS工艺晶圆的成本相对于基于6寸晶圆的III-V族工艺要低很多(3-4倍)。在现代通信集成电路中,处理器、基带以及射频收发机等模块均已使用CMOS工艺量产数十年,但由于射频PA对功率等级、线性度、效率、频率响应等特殊的要求,以及其相对收发链路中其他模拟射频器件较弱的电路复杂性,大部分的应用仍然使用分立的III-V族工艺实现,尤其是GaAs工艺。

那么,线性4G CMOS PA难度有多大?地芯科技CEO吴瑞砾举了一个很形象的例子:把一个0-1的信号,线性地放大,让0.5线性放大到5,1线性放大到10,基本上是一个线性的乘以10倍的系数放大。但在2G之前,0-1的信号则是非线性放大,无论是0.5,还是1,都是直接放大到10。从技术实现的角度,4G线性CMOS PA的技术难度就更大。这也是为何高通目前为止也未能实现4G线性CMOS PA的根本原因。

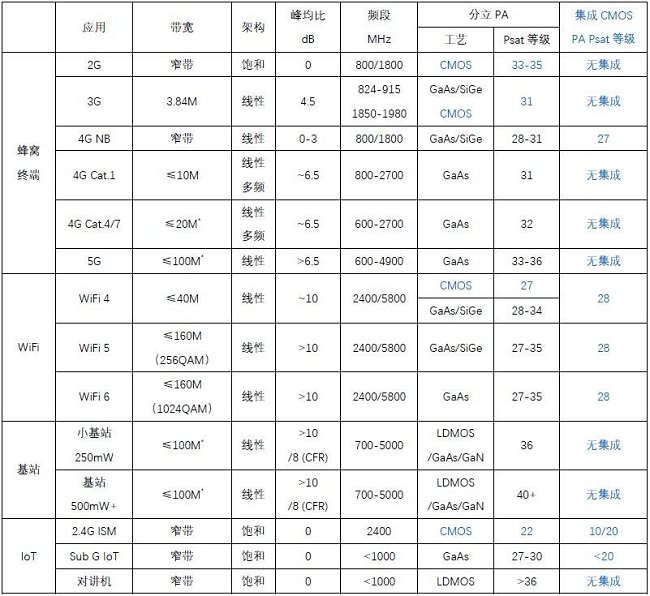

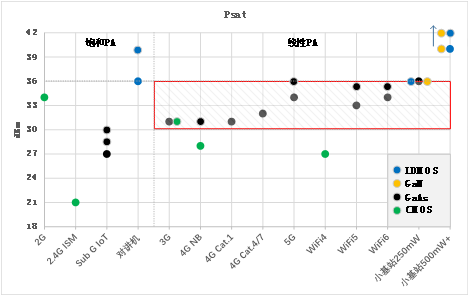

根据地芯科技研究分析资料,目前Sub 6G应用的量产产品中,不同工艺实现对射频PA不同的应用覆盖,但CMOS PA主要应用在2G/3G、WiFi 4、IoT等细分领域。对表2和图2的分析可以得出以下结论:

1.集成于SoC的CMOS PA最大Psat功率等级在28dBm左右,主要应用于小无线物联网(WiFi/蓝牙/Zigbee等各类局域IoT)以及窄带蜂窝物联网(NB-IoT);

2.CMOS工艺实现用于2G的饱和PA,Psat可达2W以上(33-35dBm);

3.GaAs 线性PA主要在Psat 30-36dBm的应用中占领大量市场;

4.Psat超过1W的线性CMOS PA只昙花一现于3G时代,并在4G多频线性PA的产业链中销声匿迹;

5.Psat超过36dBm的应用,LDMOS和GaN开始成为主流。

表2 Sub 6G应用中PA功率等级及工艺使用现状

资料来源:地芯科技(注:不考虑载波聚合)

图2 不用应用中对PA的Psat等级以及工艺现状

资料来源:地芯科技

线性CMOS PA不止步于4G!

不过,业界对线性CMOS PA工艺研发从未停滞,反而在默默耕耘与发力,不断结出累累硕果。其中,地芯科技CEO吴瑞砾就是坚定的CMOS工艺路线的支持者,当然也源于其多年CMOS PA技术研发经验。2013年,在获得美国德克萨斯理工大学电子工程硕士学位后,吴瑞砾便投身到射频领域的研发工作,曾带领团队成功开发并量产多款应用于3G/4G/IoT的功率放大器,包括世界上第一款基于体硅的线性射频功率放大器产品。回国之后,基于在CMOS PA技术上丰富的量产经验,于2018年创办了地芯科技。

“其实,目前射频前端的竞争格局是非常激烈的,大多数企业都选择一个同质化的技术路线,利用GaAs工艺来做PA。但地芯科技选择了低成本的CMOS技术路线。”吴瑞砾表示,尽管CMOS在材料上存在一些劣势,但其具有低成本、稳定的供应链等优势,而且拥有更好的导热性、漏电性能和抗静电等特性。因此,持续看好CMOS PA技术在低速率的互联网连接、大带宽Wifi、物联网终端等领域的应用前景。

“CMOS工艺提供了丰富种类的器件,以及灵活的设计性,通过巧妙的电路设计,可以通过模拟和数字的方式补偿晶体管本身的非线性。这也是CMOS PA设计最重要的课题之一。”不过,吴瑞砾也表示,Common-Source架构的CMOS PA和HBT的架构类似,其非线性实际上并非特别棘手到难以处理,主要问题在于无法承受太高的电源电压。

尽管CMOS工艺困难重重,但地芯科技一直都在挑战线性4G CMOS PA。攻克了基于击穿电压和线性度的两大技术难题,以创新的设计架构,成功推出全球首款4G的多频多模线性CMOS PA,并已经开始应用在客户的Cat.1模组产品上!

据悉,在3.4V的电源电压下,在CMOS工艺难以企及的2.5G高频段,该CMOS PA可输出32dBm的饱和功率,效率接近50%;在LTE10M 12RB的调制方式下,-38dBc UTRA ACLR的线性功率可达27.5dBbm(MPR0),FOM值接近70,比肩GaAs工艺的线性PA。在4.5V的电源电压下,Psat更是逼近34dBm,并在Psat下通过了VSWR 1:10的SOA可靠性测试。该设计成功攻克了CMOS PA可靠性和线性度的主要矛盾,预示了线性CMOS PA进入Psat为30-36dBm主流市场的可能性。

5月18日,地芯科技将在上海发布这一款支持4G的线性CMOS PA!再度证明CMOS工艺应用于射频前端创新以及进入主流射频前端市场的可能性!

未来,随着5G及万物互联的风口到来,智能手机、电脑、智能穿戴、汽车、智能机器人等都将成为信息交互的智能终端,越来越深入到人们的生活与工作中。作为这些信息交互的底层支撑技术,CMOS PA也将不断迭代升级,凭借低成本、集成化等技术优势,不断拓展更深、更广的应用场景,主宰“万物互联”时代。

本文参考:地芯科技《线性CMOS PA的挑战与机遇》

推荐阅读:旗龙